## EE 230 Fall 2006 Experiment 13

### Data Converters - Performance Limitations associated with Nonideal Properties

## **Special Instructions for this Experiment**

Since this experiment will be conducted during the last week of the semester, a report for this project will be turned in at the end of the period. There are 3 procedures listed for this experiment. You are to work sequentially on these procedures for the first 2 hours and 30 minutes of the lab period. At that time, you are to inform the TA exactly where you are in the measurements. The last 30 minutes are to be spent preparing a brief report which will be collected at the end of the laboratory period. Grades will be based upon how much progress you make on this experiment and on the brief report. Reports will only be accepted at the end of the laboratory period. If for any reason you can not spend the 3 scheduled hours working on this experiment, make arrangements in advance with your TA to attend a separate period.

**Purpose:** The purpose of this experiment is to investigate some of the limitations of data converters associated with nonideal properties of data converters. In particular, the issue of linearity as characterized by the integral nonlinearity (INL), the differential nonlinearity (DNL) and the spectral performance as characterized by the spurious free dynamic range (SFDR) will be explored.

#### **Equipment:**

Computer with MATLAB software Data from Part 4 and Part 5 of Experiment 9

#### **Background:**

Data converters are widely used as the interface between the analog environment and the digital world. Analog to Digital Converters (ADC) convert physical analog signals to digital form and Digital to Analog Converters (DAC) convert digital signals analog form. In most applications, it is expected that all information about the input signal to an ADC be preserved in the sampled outputs obtained from the ADC. Correspondingly, it is generally expected that the output of a DAC will create the desired analog signal.

Existing data converters can come very close to accomplishing these tasks provided that the right data converter is used and provided it is used properly. Even if data converters are ideal, some potential problems can occur if the resolution is not high enough or if the sampling rates are too low. In some applications, the phase of the sampling clock is also very important. Inherent limitations associated with the data conversion process associated with ideal data converters were considered in the previous experiment.

In this experiment, emphasis will be placed upon the performance capabilities and limitations associated with nonideal properties of data converters. The nonideal

properties of data converters are analogous to the nonideal properties of operational amplifiers such as finite GB, finite gain, offset voltage, and output saturation considered in previous laboratory experiments.

Linearity is one of the most important properties of data converters in many applications. If the output levels of a DAC are not uniformly spaced or if the transition points of an ADC are not uniformly spaced, the data converter will introduce nonlinearities into the output of the device that were not present in the input. These nonlinearities can affect the dc transfer characteristics of a system using the data converters and in such cases the parameters that the data converter that are of most concern are the integral nonlinearity (INL) and the differential nonlinearity (DNL). They can also affect the spectral performance of a system and in such cases the spectral performance as characterized by the total harmonic distortion (THD) and the spurious free dynamic range (SFDR) of the data converter are of most concern. In this experiment the INL, DNL, and SFDR will be considered.

## Integral and Differential Nonlinearity

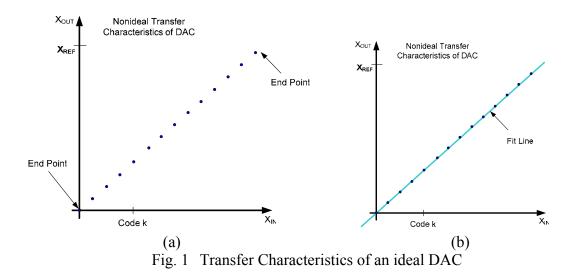

The transfer characteristics of an ideal DAC are shown in Fig. 1a. Note that the output for the smallest Boolean input corresponds to  $X_{OUT}=0$  and the output corresponding to the largest Boolean input is close to  $X_{REF}$ . More importantly, note that all transition points are co-linear. The two extreme points are called the end points. A fit line that goes through all output points of the DAC is shown in Fig. 1b.

Other ideal transfer characteristics are also possible but the key property of the ideal transfer characteristics is that the outs of the DAC all lie on a straight line.

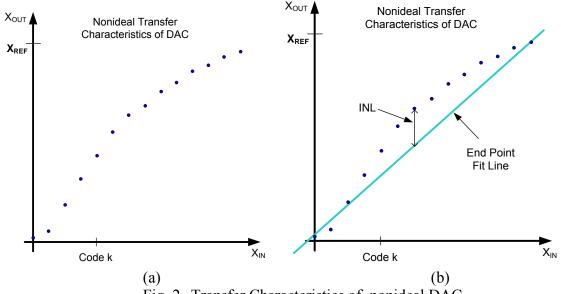

The transfer characteristics of a nonideal DAC are shown in Fig. 2a It can be observed that the transfer characteristics do not lie on a straight line. The linearity characteristics of a DAC are often defined relative to a fit line to the actual outputs of the DAC. There are many different fit lines that could be used but the data converter community generally used the end-point fit line. The end-point fit line is the line that

goes through the two extreme points in the dc transfer characteristics and is shown in Fig. 2b. Note this fit line does not go through the origin and does not have the same slope as that of the ideal fit line of Fig. 1b. The offset from passing through the origin is termed an offset error and the change in slope from that of the ideal DAC is termed a gain error.

The deviation of the actual output from the end-point fit-line output at code k is defined to be the INL at that code, that is,

$$INL_{k} = X_{OUT}(k) - X_{FIT}(k).$$

<sup>(1)</sup>

The overall INL is defined to be the maximum over k of the magnitude of all of the  $INL_k$  terms, that is,

$$\mathsf{INL} = \max_{1 \le k \le N} \left\{ \left| \mathsf{INL}_{k} \right| \right\}$$

(2)

where N is the total number of DAC input codes. The location where the deviation is maximum in the DAC of Fig. 2a is shown in Fig. 2b and designated as INL.

The INL is often designated relative to an LSB by dividing the INL by  $X_{LSB}$ . Thus, an nbit ADC with a reference of  $X_{REF}$  has an LSB of  $X_{REF}/2^n$  so the INL becomes

$$INL_{LSB} = \frac{INL}{X_{LSBF}}$$

(3)

where X<sub>LSBF</sub> is given by

$$X_{LSBF} = \frac{X_{OUT}(N) - X_{OUT}(1)}{N - 1}$$

(4)

The term  $X_{LSBF}$  is approximately  $X_{REF}/2^n$  and the distinction between these two terms which are very close is often not made and thus the INL is often expressed as

$$INL_{LSB} \cong 2^{n} \frac{INL}{X_{REF}}$$

(5)

Often the LSB subscript is omitted and it is assumed that the reader can correctly distinguish between  $I_{NL}$  and  $INL_{LSB}$  from the context in which the specification is given.

Fig. 2 Transfer Characteristics of nonideal DAC

The differential nonlinearity, DNL, at code k is defined to be the difference between the increase in the output at code k to that of code k-1 and the ideal increase relative to the fit line. That is,

$$\mathsf{DNL}_{\mathsf{k}} = \mathsf{X}_{\mathsf{OUT}}(\mathsf{k}) - \mathsf{X}_{\mathsf{OUT}}(\mathsf{k}-1) - \mathsf{X}_{\mathsf{LSBF}}$$

(6)

and, as before, it is often assumed that  $X_{LSBF}=X_{LSB}$ .

The overall DNL is defined to be the maximum over all increments of the magnitude of the  $DNL_k$  terms. That is,

$$\mathsf{DNL} = \max_{1 \le k \le N} \left\{ \left| \mathsf{DNL}_{k} \right| \right\}$$

(7)

Since there are N-1 increments, note the lower limit on the range for DNL starts with index k=2.

The definitions for the INL and the DNL for an ADC are very similar. The number of transition points for an ADC is 1 less than the number of Boolean outputs for the ADC. Thus, if an ADC has N Boolean outputs (generally  $N=2^n$  where n is the number of bits of resolution of the ADC), there will be N-1 transition points. These transition points can be designated as  $X_1, ..., X_{N-1}$ . The INL<sub>k</sub> for an ADC is defined to be the difference between the kth transition point and the kth uniformly-spaced transition points between the first and last transition points. The uniformly spaced transition points between the first and last transition point represent an end-point fit-line to the transition points. If this point is designated as  $X_{FIT}(k)$ , the INL<sub>k</sub> can be expressed as

$$INL_{k} = X_{TRANS}(k) - X_{FIT}(k)$$

<sup>(8)</sup>

It can be readily shown that the fit line is given by the expression

$$X_{\text{FIT}}(k) = X_{\text{TRANS}}(1) + \left(\frac{k-1}{N-2}\right) \frac{X_{\text{TRANS}}(N-1) - X_{\text{TRANS}}(1)}{N-2}$$

(9)

for  $1 \leq k \leq N-1$ .

The DNL for a transition point k of an ADC is defined to be the difference between the actual increment from transition point k-1 and the uniformly spaced increment. This is approximately given by the expression

$$\mathsf{DNL}_{\mathsf{k}} \cong \mathsf{X}_{\mathsf{TRANS}}(\mathsf{k}) - \mathsf{X}_{\mathsf{TRANS}}(\mathsf{k}-1) - \mathsf{X}_{\mathsf{LSB}}$$

(10)

And, as for the DAC, the DNL for an ADC is defined to be

$$\mathsf{DNL} = \max_{1 < k \le N} \left\{ \left| \mathsf{DNL}_{k} \right| \right\}$$

(11)

# Equivalent Number of Bits

If the transfer characteristics of an ADC do not lie on a straight line, the effects to the errors on a circuit using the data converter may be similar to those introduced by an ADC with less resolution. The equivalent number of bits (ENOB) is used to characterize the linearity performance of a data converter. The ENOB that is used to characterize the linearity of a data converter should not be confused with the ENOB used to characterize the signal to noise ratio (SNR) discussed earlier in this course.

Either a DAC or an ADC with n-bits of resolution should ideally be able to ideally represent a signal to within  $\pm \frac{1}{2}$ LSB for any input and should be able to represent the signal perfectly at the output points for a DAC or at the transition points for an ADC. As such, it will be assumed that  $\pm \frac{1}{2}$ LSB deviation from the ideal output or form the transition points is acceptable for an n-bit data converter but a larger deviation represents an effective degradation in resolution. With this understanding, an n-bit data converter with an INL of 1 LSB would be performing as if it were an n-1 bit data converter, one with an INL of 2 LSB would be performing at is it were an n-2 bit converter, one with an INL of 4 LSB would be performing as if it were an n-3 bit converter, etc.

Mathematically the ENOB for a data converter with n bits of resolution and an INL of  $\upsilon$  LSB can thus be expressed as

ENOB =

$$n-1 - \frac{\log_{10} \nu}{\log_{10} 2}$$

(12)

# Spectral Characterization

Any nonlinearities in the transfer characteristics of a data converter will affect the spectral performance of the data converter. Specifically, if a sinusoidal input is applied to the data converter, harmonic components will be present in the output.

For example, if the input to a data converter is

$$X_{\text{IN}} = X_{\text{M}} \sin(\omega t + \theta)$$

(13)

then the interpreted output will be of the form

$$X_{out} = A_{0} + A_{1} \sin(\omega t + \theta + \gamma_{1}) + \sum_{k=2}^{\infty} A_{k} \sin(k\omega t + \theta + \gamma_{k})$$

(14)

where Ak is the magnitude of the kth harmonic component of the ouput. The terms in the right summand represent spectral distortion and is comprised of frequency components that are not present in the input signal. The THD is generally defined to be the total power in the second and higher harmonic terms relative to the power in the fundamental. That is,

$$THD = \frac{\sum_{k=2}^{\infty} A_k^2}{A_1^2}$$

(15)

This is often expressed in decibels as

$$THD_{dB} = 10\log_{10}\left(\frac{\sum_{k=2}^{\infty}A_{k}^{2}}{A_{l}^{2}}\right)$$

(16)

Generally the contributions by the higher-order terms is negligible and the sum can be made over only the first few terms.

A second metric is often used to characterize the spectral performance and that is the spurious free dynamic range (SFDR). The SFDR is defined to be

$$SFDR = \frac{|A_{1}|}{\max_{1 < k} \{|A_{k}|\}}$$

(17)

Usually the SFDR is expressed in dB as given by the expression

$$\mathsf{SFDR}_{dB} = 20\log_{10}\left(\frac{|\mathsf{A}_1|}{\max_{1 < k} \{|\mathsf{A}_k|\}}\right) \tag{18}$$

The THD and the SFDR are generally measured by applying a sinusoidal excitation of near full-scale and then taking a large number of samples of the output waveform. From these samples, a Fourier Series representation of the output can be obtained and this Fourier Series representation is essentially that given in (14). The

following theorem provides a practical method for obtaining the Fourier Series representation of a signal x(t) from samples of the signal.

Theorem: If a periodic signal x(t) with period T=1/f is band-limited to frequency hf and if the signal is sampled N times over an integral number of periods, N<sub>P</sub>, then

$$|\mathsf{A}_{\mathsf{m}}| = \frac{2}{\mathsf{N}} |\mathsf{X}(\mathsf{mN}_{\mathsf{P}} + 1)| \qquad \text{for } 0 \le \mathsf{m} \le \mathsf{h} - 1$$

where  $\langle X(k) \rangle_{k=1}^{N-1}$  is the DFT of the sampled sequence  $\langle X(kT_s) \rangle_{k=1}^{N-1}$  where T<sub>s</sub> is the sampling period.

The sampling period is thus given by  $T_s = \frac{T \cdot N_p}{N}$ . Thus, if x(t) is band-limited

to hf, the magnitude of the coefficients of the Fourier Series Representation  $A_0$ ,  $A_1$ ,  $A_2$ ,  $A_3$ , ... are the magnitudes of the DFT elements X(0),  $X(N_P+1)$ ,  $X(2N_P+1)$ ,  $X(3N_P+1)$ , ... The Fast Fourier Transform (FFT) is a computationally efficient way for calculating the DFT, particularly when the number of samples is a power of 2. The FFT is a routine that is available in MATLAB.

Generally a prime number of periods of the input signal are sampled. It is critical that the hypothesis of the theorem be satisfied, that is, that the signal is sampled precisely over an integral number of periods of the excitation. Even a very small skew in the sampling requirements will cause major problems with using the DFT to obtain the Fourier Series coefficients.

### Part 1 INL ,DNL, and ENOB measurement of DAC

Determine the INL, DNL and the ENOB of the DAC you designed and tested in Experiment 9. Note that the ENOB can actually be larger than the resolution if the output values of the DAC have a very uniform spacing.

### Part 2 INL, DNL, and ENOB measurement of ADC

Determine the INL, DNL and the ENOB of the ADC you designed and tested in Experiment 9. Note that the ENOB can actually be larger than the resolution if the output values of the DAC have a very uniform spacing.

### Part 3 Spectral Characterization

We do not have the test equipment needed to gather samples from the output of a DAC or an ADC with sufficient accuracy to do good spectral characterization of a high-resolution DAC or ADC at this time. So, we will assume that you have an ADC with  $X_{REF} = 1V$  and a sinusoidal input signal of angular frequency 1K rad/sec was applied with a 0-P amplitude of 0.49V. Assume the output waveform of the ADC was a sampled version of the signal

$X_{OUT}(t)=0.45sin(1000t)+0.0002sin(2000t)+0.00005sin(3000t).$

Assume that 4096 samples of this output were taken over precisely 11 periods of the input.

- a) What is the THD of the output signal

- b) What is the SFDR of the output signal

- c) Determine the SFDR from Matlab and compare with the results obtained in part b)

- d) (Ex cr) Determine the SFDR from Matlab if the sampled signal is quantized to the 12-bit level.